SystemCでDE0-CVの回路を作る 構想編

SystemCを使ってDE0-CVの回路を作りたいと思ったのでやってみた。

本当はCPUの創りかたのTD4を作ろうと思ったけど、まず簡単な回路で。

動作

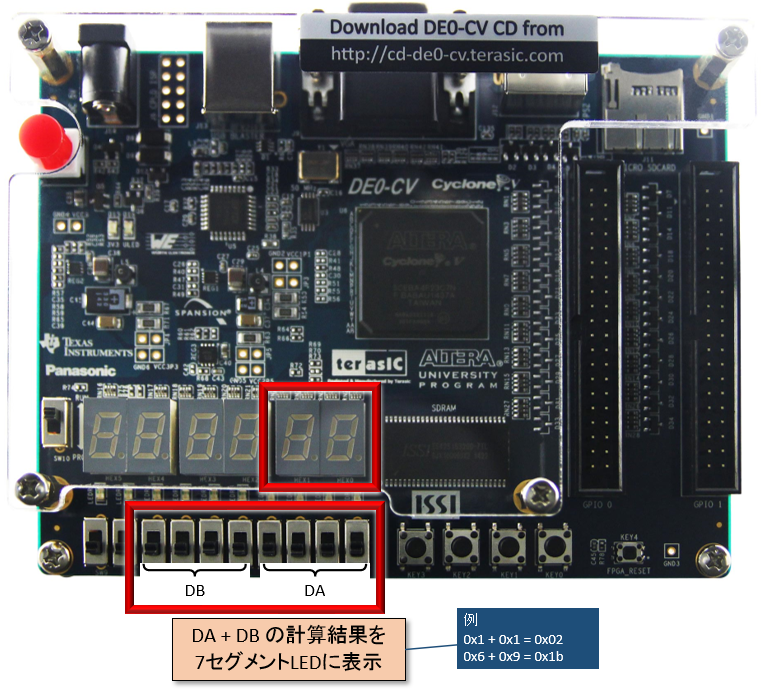

DE0-CVの左下のスイッチの下位4bitずつを加算して7セグメントLEDに表示する。

例えば、

OFF-OFF-OFF-ON OFF-OFF-OFF-ON → 02 を表示

ON-OFF-OFF-ON OFF-ON-ON-OFF → 1b を表示

みたいな感じ。

機能ブロック図

太字斜体 → 入出力ポート

[数字..数字] → bit幅 (VHDL)

<数字> → bit幅 (SystemC)

DE0_CV_TestAdderはVHDLで書かれたTopエンティティ

DE0-CV付属のDE0_CV_SystemBuilderで生成したverilog-HDLをVHDLに変更しただけのもので特に機能はない。

AdderTop以下がSystemCで作ったところ。

入力データ4bitと4bitを加算して、上位bitと下位bitで7セグメントLEDの値にエンコードしている。

それだけの回路。

実装の細かいところ

AdderModuleとSeg7EncoderはそれぞれAdderModule.cpp/hとSeg7Encoder.cpp/hにファイルを分けている。

本当はAdderTop以下に全部書いても良かったけど、Top結線のテストのためにもそんな構成にした。

工程とツール

下記の3工程とツールを使った。

SystemCをRTLに合成するツールで使えるのがVivadoHLSしかなかった……。

Intel(Altera)のFPGA用RTLをXilinxのVivadoで作るというへんな工程に。

会社だとNECのCyberWorkBenchを使ってるんだけど、個人では使えないしな。

次回は環境構築編を予定